# **Crawl-Space** Computing

# **Crawl-Space** Computing

Lawrence J. Dickson

Cooperating programs that don't hide your data while they are working on it

(including a guide to the Connel toolset)

© 2014 Lawrence J. Dickson.

This work is licensed under a Creative Commons Attribution-NonCommercial 3.0 Unported License. To view a copy of this license, visit creativecommons.org at http://creativecommons.org/licenses/by-nc/3.0 or send a letter to Creative Commons, 444 Castro Street, Suite 900, Mountain View, CA 94041, USA.

All of the book's source code and pseudocode is licensed under the Apache License, Version 2.0. You may obtain a copy of this License from the Apache Software Foundation at http://www.apache.org/licenses/LICENSE-2.0

Unless required by applicable law or agreed to in writing, any source code or pseudocode in this book or ebook is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the Apache License, Version 2.0, for the specific language governing permissions and limitations under the License.

This book was published with the crucial aid of several people.

| Thomas L. Dickson    | Production and Typesetting |

|----------------------|----------------------------|

| Alice K. Dickson     | Art and Illustrations      |

| Elizabeth M. Dickson | Cover Art                  |

My thanks go also to my wife Jeanne C. Dickson, without whose encouragement I would have bogged down, and to the Kickstarter organization, which provided me a path out of the post-2008 funding desert.

This book was typset using pdfEATEX on  $7'' \times 10''$  paper using EATEX and the memoir package (among others) on May 5, 2014. This is revision 253.

Printed in the USA and other locations

Fierce Press National City, CA United States ISBN-13: 978-0-9666440-1-2 ISBN-10: 0966644018

# Dedication

This book is dedicated to my father and mother:

LAWRENCE EDWARD DICKSON September 17, 1913–January 9, 1981

ELIZABETH MARY HELINA DICKSON November 14, 1920–August 8, 1976

They brought me and my sisters up, without deference to prevailing trends, on an acre in north Seattle. Everything that is pithy and countercultural in my book and life arises from their original inspiration.

# Major Contributors

**Partner** Adrianus Warmenhoven

> Angels Alexandru Nedel Kyle Cassidy

# Patrons

Roger Wagner Dennis Roos Richard Miller Rob Fryer Elizabeth Dickson

This book is part of a Kickstarter project. Without the support, and the guidance on priorities, of the above major backers, it could never have happened. For whatever enduring value you find in these pages, please thank the people above.

# Preface

The growth of scientific knowledge has obviously spurred a massive explosion of technology. But, the driving spirit of science is not to change the world but to understand it.

—Kwame Appiah, quoted by Bill Cowan, University of Waterloo, Canada

The purpose of this book is to leave a legacy.

This purpose connects to a situation in which we, the world of creative programming, now find ourselves. Together, the purpose and the situation are going to determine the shape of this book. I'm saying this right here, early on, because it is rather an unusual shape, more tilted (at first) toward "creative" than toward "programming." So bear with me while I explain.

### **Recovery from monoculture**

For the last two decades, I have been like a guide keeping open the trail to Nova Scotia while the covered wagons all go thundering off to California. Nothing about the science of computing has changed, but the way people talk has gradually altered, year by year. Computer programs and even computing languages are a subset of "the way people talk." And many years of slow change can sum up to quite a shift.

My roots go back to the seventies and earlier, to an "age of science." People were discovering the Van Allen Belts and bringing back rocks from the Moon. Computing was in its infancy, although the *science* of numerical algorithms, as represented by Donald Knuth, was well underway. By contrast, in 2014 we have been for many years in an "age of technology," and computing is a trillion-dollar industry. But positive feedback, typical of commercial success, has led to a narrowing of technique.

Computers obey both command and nature, but command has been the focus of development since the early 1990s. Physical nature has a wide, accessible, village-like structure of territorial entities communicating across boundaries over time. This is deliberately hidden in the deep, centralized, legalistic command structure called "abstraction," which thus easily appears to produce instant, universal results at will.

The results are easy to see. Things like multiple choice, picking from a list, filling in the blanks, doing what the user interface wants—these all go fast

and easy. But what if the task is different? What if the data does not fit, or you need an ellipse instead of a rectangle, or the mouse can't do a fine enough job? Then although it is clear that all the necessary data and capabilities are there, ease of use becomes extreme lack of flexibility. All of a sudden, THE PROGRAM STANDS BETWEEN YOU AND YOUR DATA.

It's important here not to be deceived by appearances. A massive increase in quantity (not to mention flashiness) can leave the impression that "things are busting out all over" when in fact nearly the opposite is true. It's like the huge increase in supply of potatoes in pre-1847 Ireland, but they were all one kind of potato, susceptible to one rot. And since the coding problem is all one kind of thinking—a monoculture of the mind—I needed to step back and take thought myself about how to leave a legacy that fights it.

First, it's clear I have to use tools that date from before the convergence. Practically speaking, that means C, a 1970s-era language that still is supported almost everywhere, thanks to its low-level flexibility. In addition, there are operating system usages, like **bash** (in Linux/Unix/BSD) and BATCH (the old name for scripting in DOS and Windows), that have proved remarkably persistent. The reason is mainly that the programming of servers demands them.

In addition, I have to use an approach that can ease the modern programmer out of the monocultural mindset. This means going behind programming to things and what they actually do. That is why the first few chapters of this book will have an almost artistic feel. Only after assembling these kindergarten blocks can I re-enter the world of programming, this time with specific instructions on how to make it do what Wide Computing wants.

Luckily, it turns out that is a pretty good description of what my legacy teaching is trying to save: things, and what they actually do.

#### What do you need to know?

Because of my artistic lead chapters, the answer to this question is: *not much.* In fact, all I really ask is a scientific bent of mind. Things have consequences! Also needed is your willingness to have patience while you work out these consequences.

An experienced programmer or computer science student may actually need to *unlearn* some things. Almost always, when a word has a modern computing meaning and a more general naive meaning, I mean the latter. I do my best to avoid these. For instance, I use "piece" where the more natural term would be "component," which unfortunately has an object-oriented meaning quite different from what I want to say. Still, some will sneak through.

If I succeed at my task, the complete newbie will find himself or herself able to program more and more as the chapters advance. This is because the thing, and what it needs to do, cause questions to arise. These, in turn, require research and design, before a word of code is written. The program will break into more than one piece, and data will flow between them, with data rate requirements. Each piece is simple (even if its algorithms are not), and the data passing between pieces is also simple. Each piece can be tested *by itself*, and when all are put together, you will suddenly find you have a working device.

After all, I'm not really a programmer. I'm a mathematician, and I like to know why things work. Since I'm a lazy mathematician, I like it to be *obvious* why things work. It's amazing how easy programming becomes when you break it down into little things that obviously work. That includes fast, powerful, rocket-science programs, because power and mystery are not the same thing!

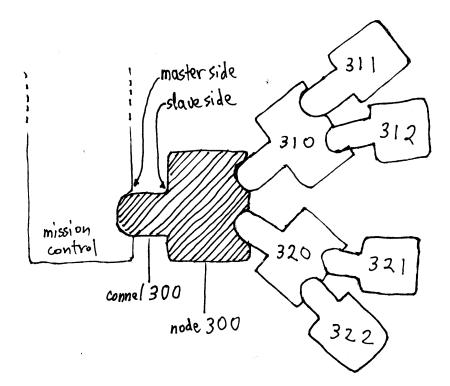

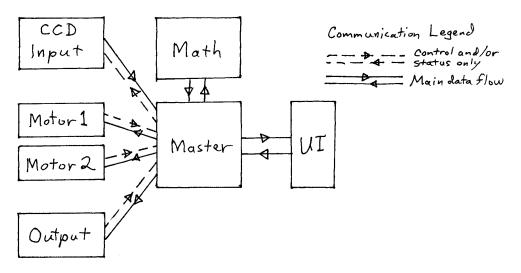

# Connel

The C toolset Connel goes with this book. Although Connel is not necessary to apply this book's techniques, it makes things easier, especially when a modern, UI-centered operating system has to talk to hardware and embedded code or code on other machines. Connel, which is named after "connector link," compiles and runs *without change* both on Linux and Windows, and the resulting programs can communicate (Windows to Windows, Linux to Linux, or Windows to Linux). Connel is also designed to communicate with "alien" code and hardware, whether it's a UI-based program in any language, or embedded code running on hardware that may not have an operating system or even a standard compiler. Connel also cooperates with virtualizers like VMWare to allow programs on different virtual machines to talk to each other.

The beauty of Connel is that you don't have to learn a new protocol for each communicating application. Often, you don't even have to recompile the code. This is because the talking machinery of Crawl-Space Computing behaves the same (in the state machine sense) between any communicating pair, whether software or hardware. In fact, you don't even need both sides of the communicating pair: you can substitute a *dummy* on one side, and the other side will run at full speed and not even know the difference. In addition, you can "mix and match" real working modules at will, and all your data is always completely under your control as it passes from one module to another.

### Acknowledgements

The amazing success of my Kickstarter is what makes it possible for me to try to hand over this legacy. Credit goes to a lot of people. I've listed some tersely in the preceding pages, but it does not do them justice.

This project would not be where it is without the work of many others. I wish to thank my daughters Elizabeth and Alice and my wife Jeanne for all their help with the video. It could not have happened without them. Also, I thank my son Tom and my colleagues William and Dave Swanson, Rob Fryer and Trey Hunner for advice in development, and especially for the chance to do real robotics and satellite science. I am more of a theoretician, but with these other creative people pitching in, some real and impressive things are getting done.

I wish to recognize the contribution of the scientists, mostly from England and Europe, of the occam-com list. For decades, since before the eclipse of the Transputer, they have carried the torch for Communicating Sequential Processes (CSP) and related Wide Computing projects, while to be sure allowing a little abstraction to creep in. Discussions with them have stimulated me, both in my work leading to this book (including errata found by Anne Van Rossum), and in my ITOCA patent work. In particular I wish to remember my colleague Michael Poole, author of the Transputer Development System (TDS), who passed away recently.

Several major contributors, of technology and exposure as well as finances, are already carrying this beyond anything I could have anticipated. I've asked around among them about setting up a Wide Computing community to accomplish more than I can alone. Of these, four wish their work to be publicly mentioned, while others prefer to remain behind the scenes.

Adrianus Warmenhoven is the leader who, among other things, came up with the Raspberry Pi stretch goal. Contacting him thousands of miles away shows what a brilliant thing Kickstarter is. He already has a group of people who, in many cases, state what I am after better than I can myself.

William Swanson is my longstanding colleague at MeasureBot3D LLC, the robotics invention startup whose computing side he has been leading and I have been aiding. As a brilliant young embedded programmer, hardware designer, and language creator, he has made frequent contributions to my design thoughts. The latest was an introduction to XCB and to Windows graphics, which helped get the Graphics Slave off to a good start.

Trey Hunner is the San Diego organizer who has put me in touch with so many key people, including Roger Wagner and Tero Kukola, not to mention a local business incubator that may be in a future bigger than one desk at home. Without Trey, I would never have set about Kickstarter.

Rob Fryer is an eager inventor and engineering pioneer whom I've known for years. He widens my horizons to things like the Kicksat project which will include a satellite by Rob's team. This challenge has been a fertile source of Wide Computing ideas - as my WORLDCOMP 2013 presentation showed.

There are others, whom I can't mention here, but you know who you are, and please be assured of my gratitude! They have provided even more directions, like OSC. I must focus on the promised rewards, so the more initiative you all take, the happier I am.

We made it - and I must say that the response was far better than I ever really expected! I look forward to working with you all, and going beyond the mere posting of the rewards. I think I will be able to declare some "skosh room" and do the Raspberry Pi port anyway. One generous backer has already provided hardware, and others have expressed great interest. I may have to call for help or stretch the time a bit.

Finally, I'd like to thank the Kickstarter organization itself. Reaching all around the world to a group of people who don't know each other but are trying to save the same thing is an amazing accomplishment, and it is the Kickstarter design that made it possible. Funding anything countercultural in the post-2008 desert is also an amazing accomplishment, and the Kickstarter design made that possible too. Every call for help to Kickstarter personnel got a prompt and effective response, and their advice, in FAQ and elsewhere, was unfailingly wise, as unfolding events proved to this business newbie.

# Contents

| $\mathbf{P}$ | refac | e ix                                                       |

|--------------|-------|------------------------------------------------------------|

|              | Reco  | overy from monoculture                                     |

|              | Wha   | at do you need to know?                                    |

|              | Con   | nel                                                        |

|              |       | nowledgements                                              |

| 1            | Intr  | oduction 1                                                 |

|              | 1.1   | Approach                                                   |

|              | 1.2   | What is Wide Computing?                                    |

|              | 1.3   | Why?                                                       |

|              | 1.4   | Drill down                                                 |

|              | 1.5   | References                                                 |

| <b>2</b>     | Firs  | at Wave 27                                                 |

|              | 2.1   | First Wave technique                                       |

|              | 2.2   | Basic communication                                        |

|              | 2.3   | The alternation, also known as select()                    |

|              |       | or WaitForMultipleObjects()                                |

|              | 2.4   | Some kinds of communication channels and events            |

|              | 2.5   | Example: orchard sensors (thank you, Roger Wagner) 35      |

|              | 2.6   | Example: satellite CDMA receiver (thank you, Rob Fryer) 40 |

|              | 2.7   | Summary 48                                                 |

|              | 2.8   | References                                                 |

| 3            | Тоо   | ls 55                                                      |

|              | 3.1   | Principles behind the tools                                |

|              | 3.2   | Wide pseudocoding and the structure of occam               |

|              | 3.3   | Folding editor                                             |

|              | 3.4   | Introduction to Connel                                     |

|              | 3.5   | Connel library calls                                       |

|              | 3.6   | Sample program using Connel                                |

|              | 3.7   | Standard third party tools                                 |

|              | 3.8   | References                                                 |

| <b>4</b> | Second Wave    |                                                       |     |

|----------|----------------|-------------------------------------------------------|-----|

|          | 4.1            | The step from design to pseudocode                    | 109 |

|          | 4.2            | Focused pseudocoding of some FIFOs                    | 111 |

|          | 4.3            | Data-flow pseudocoding of the orchard sensor system   | 121 |

|          | 4.4            | Data-flow pseudocoding of the satellite CDMA receiver |     |

|          | 4.5            | References                                            |     |

| <b>5</b> | Pro            | gramming Using Connel                                 | 183 |

|          | 5.1            | How to use Connel tools                               | 183 |

|          | 5.2            | Rundown of pseudocode for sercomio                    | 185 |

|          | 5.3            | tapper: a client/server system                        | 187 |

|          | 5.4            | sockspy: a channel spy program                        | 207 |

|          | 5.5            | Other sketches                                        |     |

|          | 5.6            | References                                            |     |

| 6 Wie    |                | le Embedded Programming                               | 235 |

|          | 6.1            | Embedded essence: time flow                           | 235 |

|          | 6.2            | Simple and universal operating systems                | 254 |

|          | 6.3            | Details of embedded design                            | 263 |

|          | 6.4            | References                                            | 277 |

| Ac       | erony          | ms and Abbreviations                                  | 279 |

| In       | $\mathbf{dex}$ |                                                       | 283 |

# Introduction to Wide Computing

#### Abstract

1

The purpose of this chapter is to introduce a 2014-era computing enthusiast to Wide Computing—the why, the how, and the theory. I will follow an elementary, even naive, approach for two reasons. First, I want to reach as wide an audience as possible. And second, a key feature of Wide Computing is that it reduces abstraction to a minimum. You get your hands on serious data and do useful projects without mastering a six-volume API.

- $\alpha$ —time, space, and parallel from hobbies to space science

- $\beta$ —get rid of hiccups

- $\gamma$ —hardware/software equivalence

- $\delta$ —natural data and timing gate keepers set you free

- $\epsilon$ —flatten out the difficulty curve for complex projects

- $\zeta$ —the duality of Wide versus Deep

- $\eta$ —tools that open doors

- $\theta$ —terms that everyone can understand

### 1.1 Approach

The practical approach taken in this book, and in this introduction, is "advancing waves." Each wave reaches a certain level of utility, with a number of forward references and partially worked-out concepts. These raise a number of questions, which lead to a discussion of theory and specifics that illuminate the foundations of the next wave.

The usual Deep introductory approach is to offer hands-on coding (or at least filling in the blanks) of a tiny, restricted "Hello World" program, and then to proceed through targeted features. (Compare [9].) The Wide approach embraces the entire world of computing from the very beginning, and focuses in by stages on details that will allow actual programming of the project. This will support *any* project, and gain control of *all* the data, not just what the author or language designer discloses.

Each task under this approach therefore starts with a design stage (like essay-writing instead of filling in the blanks), and the design is based on theory. So my first job will be to introduce you to the theory. The beauty of this theory is that it is simple, naive, and short—the opposite of what people now expect of a computing paradigm! And it is capable of doing every computing task.

| ITEM                    | DEEP EMPHASIS                                           | WIDE EMPHASIS                                                        |

|-------------------------|---------------------------------------------------------|----------------------------------------------------------------------|

| Resource allocation     | Shared<br>Dynamic<br>System-controlled<br>Infinite pool | Distributed<br>Static<br>Explicitly programmed<br>Explicitly limited |

| Configuration decisions | Run time                                                | Load time                                                            |

| Initial state           | State of all<br>enclosing callers                       | Explicit load-time<br>setup parameters                               |

| Component life          | During call only                                        | Eternal                                                              |

| Typical task ordering   | Stack                                                   | FIFO                                                                 |

| Normal stack state      | Deep                                                    | Empty                                                                |

| Information passing     | Calling sequence,<br>global variables                   | Process-to-process<br>(channel) transmission                         |

| Program control         | Serial                                                  | Parallel                                                             |

| Model                   | Compiler parse                                          | Connected hardware                                                   |

Table 1.1: Contrast between paradigms

### 1.2 What is Wide Computing?

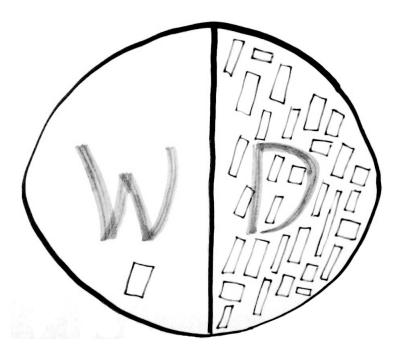

Wide (Crawl-Space) Computing is the technique of programming independent pieces, and exposing, at the top level, the communication and timing connections carrying all their shared data. It contrasts with Deep (Concrete-Slab) Computing, which exposes a single face of control and underlays this with many hidden layers of callable program components able to perform parts of the tasks desired. Wide is naturalistic, while Deep is legalistic.

To drill down into the implications of this, see Table 1.1. This is, except for the column headers, identical to a table I published in a 1996 paper [3]. The Deep trend established then has (except for a few outliers like map-reduce, GPGPU and Go) only continued, adding one or two layers in many computing languages, as in [9].

Every one of the rows in Table 1.1 is related to independence of the pieces and/or exposure of the communications. For instance, deeply nested calls (which correspond to multiple inheritances in object-oriented languages) are easily done deep in a stack, but those deep stacks are not friendly to context switches that support independent program pieces (multitasking).

To take another example, the independent pieces of Wide Computing clearly require parallel program control. By contrast, the single face of control (typically a graphical user interface) preferred by the Deep model imposes a single timeline and is therefore locked into the methodology of serial programming. This is the source of the common opinion that massively parallel programming is a task of fantastic difficulty. That's only true if you insist on the Deep model. Non-programmers (like shoppers in a store) do massively parallel tasks all the time without thinking.

The rest of Table 1.1 will become clear as we progress. Right now, there are already questions that need to be answered.

# 1.3 Why?

To get started on the **why** of Wide Computing, I'd suggest you glance at two references. First, look at the 2014 cutting edge of Deep in [1] (thank you, Roger Wagner), and then look at Wide as done in 1993—[10] Figures 13 and 17. On the one hand you have extreme obscurity based on convoluted design (callbacks), while on the other you have a design picture that anybody can understand, with arrows meaning real data flow between real entities. Think of them as villages with roads carrying traffic.

You can do any computing task with the Wide approach, as is rather obvious, since both microprocessors and human society are built that way. But after twenty years of monoculture, the computing world "speaks Deep," leaving the problem of getting from here to there. This book, and Connel, offer shortcuts to make this happen. This section will introduce you to the reasons why it's worth the effort.

# **1.3.1** $\alpha$ —Time, space, and parallel: from hobbies to space science

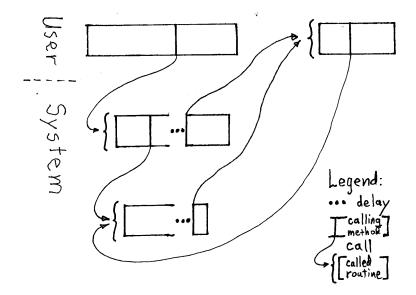

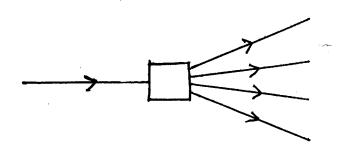

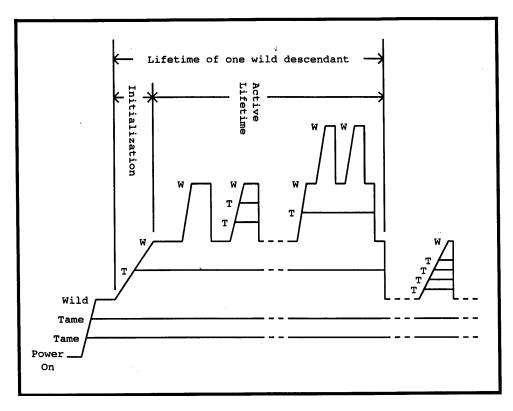

Wide computing works within time, while Deep computing is designed as if everything were instantaneous. Because delays do exist, and are significant, Deep computing requires *callbacks*. The low-level, "reused" system driver code that hides timing and data input/output must call high-level user functions to deal with the specifics of the program, as in Figure 1.1.

Notice that this requires passing a function as an argument to a driver (so-called "first-class functions"), which has bad implications for security and

Figure 1.1: Deep calling structure with callback

predictable behavior. This introduces variability in the hidden drivers, which in Object Oriented programming is called "inheritance" and "polymorphism," thus making a namespace-centric feature out of a design flaw. Notice also the existence of circular paths, which can lead to resource trouble, especially since the deeper behavior of driver code is usually obscure.

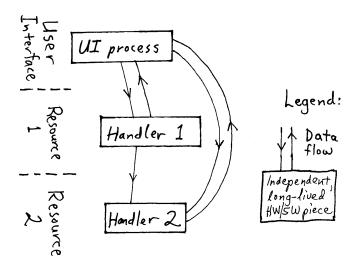

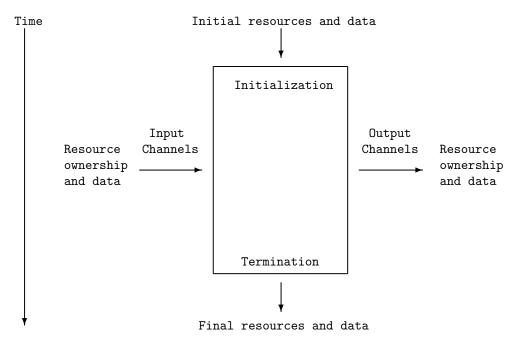

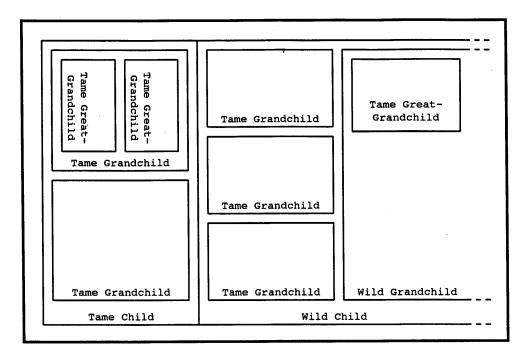

Wide computing handles the same problem in Figure 1.2. Here the contextdependent method calls are eliminated, and replaced with independent programs ruling distinct resources ("pieces"). Notice that the top piece subsumes *both the user method and the callback*. In place of call arrows we get data-flow arrows, allowing natural control of all the state complexity that gets scattered among the Deep methods and drivers. Each piece can be tested separately, and all the data flow through the arrows is accessible.

Because **time** is OK in Wide programming, the pieces of Figure 1.2 are relaxed about blocking. In fact, they deliberately exploit it for control purposes, which can easily be programmed in. And **space** (in the territorial sense of ownership, rather than sharing, of resources) comes natural to independent "workers" tasked with parts of a project. Finally, the entire structure of Figure 1.2 is obviously **parallel**, in contrast to the Deep structure, which is straining to preserve the metaphor of nested calls on a single CPU.

There it is, in a nutshell. From hobbies to space science should be obvious now. Think of any project of that sort, and it breaks down, *and breaks*

Figure 1.2: Wide structure of independent pieces

*down naturally*, into a more extensive version of Figure 1.2. In fact, Wide pieces improve on code reuse. They allow whole device reuse, independent of version and operating system, and complete control of data flowing between program parts.

The only question remaining is: can you do this kind of stuff—with modern tools? And the answer is: you are forced to do it, because time and resourcespace dominate every project. You can follow the dictates of "advanced" tools and agonize through every step, struggling upstream against the tools' Deep bias. Or you can deliberately impose Wide structure *from the beginning of the project*, selecting tools that fit the design. Making this possible is the purpose of Connel, and of this book.

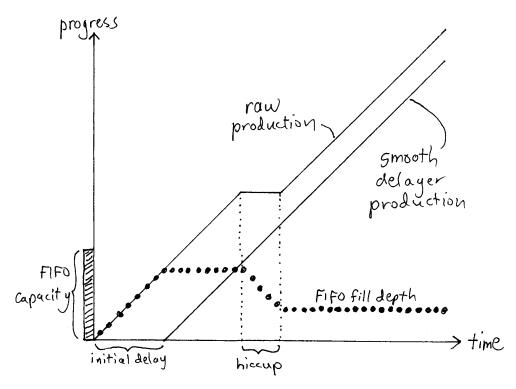

#### 1.3.2 $\beta$ — Get rid of hiccups

Building software to race as fast as possible through a problem leads to hiccups, or glitches in the flow, because irregular input and natural variation cause batches to come ready all at once, with time gaps in between. The Deep paradigm refuses to deal realistically with time, and therefore it keeps falling into this trap. It's built into Deep DNA, so to speak. Remember the early computer games that were ruined when X86 CPUs *increased* their clock speed?

Only Crawl-Space Computing can assure no hiccups, because only Crawl-Space Computing puts the data flow plumbing on the outside. Once all the data flow (video, music, robot actuator feedback) is there where you can pass

Figure 1.3: Hardware/software equivalent communication

it through your traffic meter, you can design exquisitely smooth production. I'll detail the solution later in the book.

One point needs to be made. Some people complain that the data passing overhead of the Wide model kills the efficiency of the program, causing Figure 1.2 to limp along behind Figure 1.1 forever. This is rarely so, and any randomintensive database case that suffers from such a Deep requirement can be enclosed in one box in Figure 1.2 (a so-called *harness*) and the rest of the world can treat it as a source. For everything else, communication overhead can be made minor, because immense hardware and protocol effort has gone into making that so.

The best is the enemy of the good. If you insist on the highest altitude, you have one possible point and no room for maneuver. My rule of thumb is that one to five percent can be yielded to Wide overhead, as this is vanishingly small compared to Moore's Law variations.

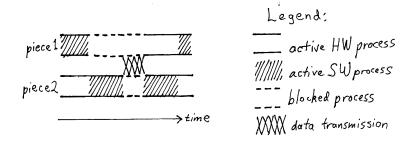

#### 1.3.3 $\gamma$ —Hardware/software equivalence

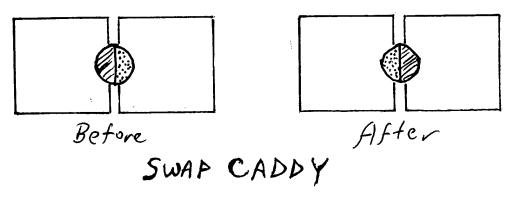

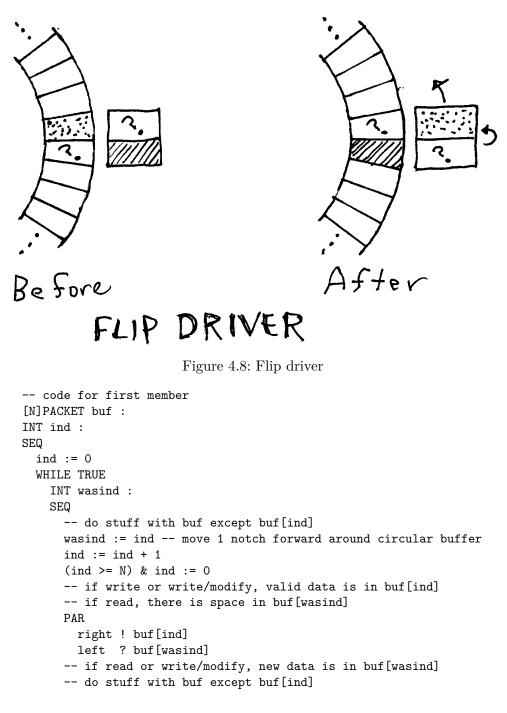

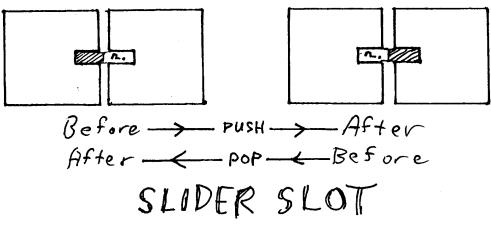

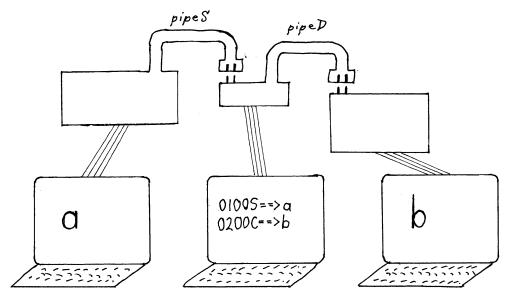

The mighty Communicating Sequential Processes (CSP) model (see [8]), as expressed in occam ([6]) and the Transputer, leads to hardware/software equivalence. This means equivalence of multitasking (lots of programs running under the OS) and multiprocessing (lots of embedded thingies helping you out), and interchangeability within these classes. In the book, I develop this even further with "move"-type operations such as the swap caddy, the flip driver, and the slider slot, described in the Second Wave chapter.

Figure 1.3 shows a simple case of hardware/software equivalence, an unconditional point-to-point communication. The direction is unimportant; what matters is that **piece1** came ready before **piece2**. The hardware version could be on two separate processors connected by wires; the software version could

Figure 1.4: Harness with data rerouting

be multitasked on a uniprocessor. The machinery of data transmission could tie up both, one, or even neither (DMA) of the processes' CPU cycles. The state-machine behavior is not implementation-dependent, though speed is.

All the other occam-like constructs used in Wide programming, such as parallels and alternations (select()), show similar hardware/software equivalence. Connel is also designed this way. The power of this is immense, as it yields also hardware/hardware equivalence and software/software equivalence, allowing easy mix and match operations with Wide pieces, often without even a recompile.

#### 1.3.4 $\delta$ —Natural data and timing gatekeepers set you free

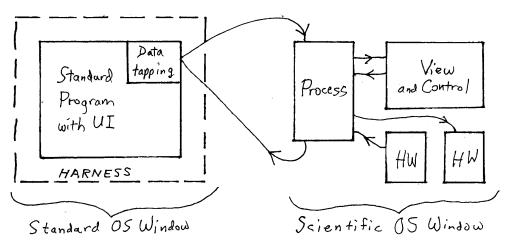

Modern apps and mystery programs (the kind found on the "cloud") cause discouragement, because the programmer or artist feels trapped in the labyrinth hiding his data. But every program has to output at some point. This is where Wide designs can gain control. You draw a line around the big, tangled thing, and start to extract what you need.

What I call *gatekeepers* are the focus of Connel. They live in very general programming spaces (Linux and Windows) and are meant to operate in tandem with undigested hunks like UIs and UI-based programs. Each program has a way of packaging and outputting data, whether a "save" or an export, and each OS has ways of transmitting this from program to program, even if scripts and canned UI sequences have to be used. GUIs even offer ways, like Automator in the Mac, to script their UI sequences, though this capability is little known

(thank you, Tom Dickson).

Drawing a line around the standard "app" in this way, and causing controlled data flow in both directions across this line, is called a HARNESS. Once the data has passed coherently under control of your Wide pieces, which live outside the harness on the right-hand side of Figure 1.4, and are connected with connector links (connels), you can shout out "FREE AT LAST!" and begin to really create.

Here I define a (lowercase) *connel* to be a practical, explicitly named or addressed device for carrying data in blocking FIFO fashion from one piece to another. It can be either hardware or software.

The two OS Windows of Figure 1.4 can be windows in one OS, or whole virtual machines, or connected physical machines. Because the gatekeepers (like select() among sockets or serial channels) are responsive, you do not have to restrict yourself to batch runs. You can display it, you can watch it flow, you can do science on it, you can do subtle modifications and then pass it back to the app.

The image of *villages connected by roads* is the complete picture of your project. The reason I created Connel, and the way it works best, is to make the app or UI be just one village and give freedom to make several other villages, all totally according to your specs, and responsive to whatever kind of independent software or embedded hardware you want to connect up. It turns out that the important data can always be reduced to a simple form, it flows fast down the "roads," and you can watch all of this flow and time it precisely.

#### 1.3.5 $\epsilon$ —Flatten out the difficulty curve for complex projects

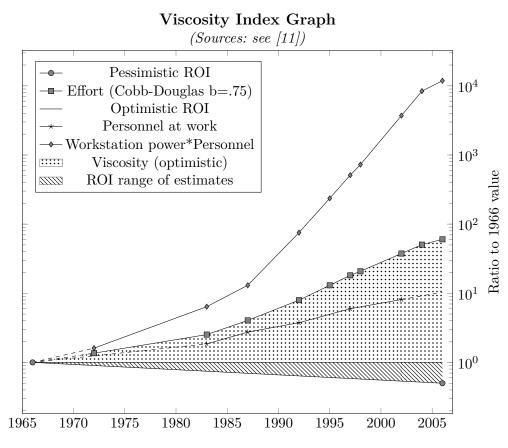

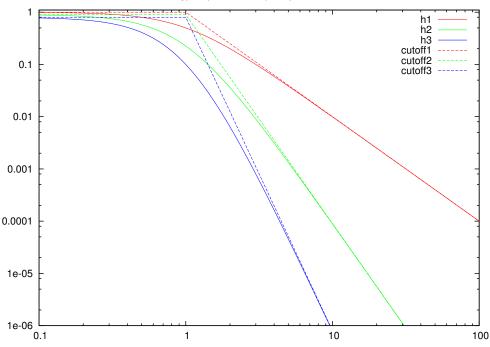

Everyone has heard of major disasters in software projects, the latest at this writing being the \$500,000,000 "Obamacare rollout" in 2013. Less well known is the relative fruitfulness of computing development in the Space Age of the 1960s and early 1970s, with fewer engineers and far poorer equipment. Figure 1.5 is the result of some research I did for DARPA in 2007, showing that *development viscosity*, defined as amount of effort per unit of improvement, has conservatively increased 60 times (not 60%) since 1966.

The reason is the factorial (worse than exponential) difficulty of Deep development, where everything has to relate to all of past history, taken in any order. Typically, user-level developers throw up their hands at understanding the consequences of all the hidden code invoked by their modules. If the target project is anything but incremental, this leads to "Obamacare disasters." You will notice this almost always, when an important customer utility installs major new software.

Figure 1.5: Massive increase in development viscosity

The Wide, communicating village model flattens this difficulty curve to linear. To convince yourself of this, use Obamacare as an example. Just devise a data flow description of the health care signup, analogous to Figure 1.2. From subscribers to insurance companies, it's not much more complex than Figure 1.2, and its physical bigness is soluble by repetitive construction methods.

With harnesses and completely described data flow, many developers (past and present) can work together and not bog down in each other's complexity. Every piece can continually be tested independently of all others, creating a comfort level that extends across every nested depth of the design. Standardize/send/particularize is a trivial overhead compared to this boon.

As unplanned new requirements pour in, the project adjusts without a complexity explosion. (An analogy that shows this is the expansion of pioneering settlement networks in the 1800s.) All particularizations, such as changing

Figure 1.6: Duality

apps, OS versions, and data formats, are quarantined within their harnesses, at worst resulting in packet protocol additions, easily coordinated between two sides of a harness edge. So the easy development leads to trivial maintenance (my DBA name is "Lost Art of Zero Maintenance").

### 1.3.6 $\zeta$ —The duality of Wide versus Deep

My claim of a *duality* is a huge claim, because it implies that the Deep monoculture has neglected half the "development territory." Figure 1.6 is **realistic!**

Close examination of Table 1.1 gives details of the duality. Both in nesting development and spreading applications, each Deep approach has a dual Wide approach. See [7], in which the original Object-Oriented terminology, which is nowadays fully Deep and namespace-centric in its applications, refers in 1993 to the Wide entities implied naively by its nomenclature. (Minor namespace changes in established Deep languages, hiding tools like C malloc, hijacked the Object-Oriented approach in the early 1990s.)

Perhaps the most unintuitive example of this duality is call/return, typically a Deep action involving pushing and popping a stack. It's a surprise to most people that there is a Wide dual, fully implemented in Transputer occam, which uses no stack but places the call information in a process workspace, and does a jump/jump-back. (A Transputer has a three-word stack used only for interrupts.) This allows calls to work well in parallel constructs, and can be set up on any processor with a workspace pointer, like the X86 register DS.

Graphical user interfaces display the duality very strongly. The *user experience* of a GUI is completely Wide: the mouse pointer is moved to a **territory** to grant focus or make a selection or an input. The territorialism is 3D, with windows lying under other windows. However, standard GUI *programming* "maps" this Wide experience onto a unified Deep block of code, in which the visible territories do not have an independent existence but are implemented by an event-based Deep call and callback structure.

This Deep abstraction of the GUI can have highly anti-intuitive results if not programmed very carefully (where "very carefully" means "in a way that fits the territorial intuition"). Thus, GUIs are one case where moving to the Wide side of the duality could create a great simplification and increase of robustness at a stroke. Because it's human speed, the overhead caused by extra communications would be insignificant.

#### 1.3.7 $\eta$ —Tools that open doors

An infuriating experience that is growing ever more common (thank you, Tero Kukola, for making me aware of this) is the tool that acts as a gated community, where you do not control the gate. You have "access" (or refusal of access) taking the place of ownership. You find yourself being moved to the "cloud" where your work is stored mysteriously and dished up only by a program to which you must pay subscription fees. Instead of being located clearly in a file system under your control, it is accessible vaguely by a search.

This is an extension of the click-on-file system, developed much earlier, where a *file* (your created object) is associated one-to-one with a *program* that, by implication, is always used on that file. From a scientific point of view, that is absurd. Your data should lie open to you to use in ways limited only by your imagination. It should be so clear that you can organize work on it by hand.

The Crawl-Space or connected village model of Wide computing is clearly sympathetic with this ideal, while the convoluted Deep model, with its important hidden details, is prone to access limitations. Two "orthogonal" features supported here encourage massively accessible data. One is *pseudocoding*, in which an occam-like dialect is used to define precisely the state machine behavior of the program. I use occam because, line for line, it is much richer than C in state machine capability, being designed to support Communicating Sequential Process (CSP) program structure. The other is *packet protocols*, which actually define the data as it is passed, allowing complete assurance that the information suffices for the project requirements.

In the book, I go into detail about pseudocoding, but leave the packet protocols (which are well known in standard computing) up to you. In addition, I offer some detail about standard tools, such as the **make** process of compiling, and the text files behind an Integrated Development Environment. By proceeding in this direction, you, the developer, can be freed from dependency on any specific tool.

#### 1.3.8 $\theta$ —Terms that everyone can understand

Wide Computing is friendly to a naive approach because its behavior displays a strong analogy to connected *physical* devices. The book bolsters this by insisting on the hardware/software equivalence in its extensions of occam, even if the hardware analogy is rather impractical. The reason for this is that the hardware analogy forms an anchor, imposing behavior limitations that prevent many forms of "going nuts" that are typical of Deep (legalistic) computing algorithms. It also prevents invalid metaphor, a source of deep-seated bugs that is in the DNA of most standard computing. For a detailed discussion of this, see my white paper [4].

Being a mathematician, I have a personal preference for the terminology of mathematics and physical science. I also have a hard time following abstract Computer Science of the sort found in [1]. The entire book is designed for a non-Computer Science major. Anyone who can hack code to do a science project ought to be able to follow my presentation.

I admit that there are places in the book where the mathematics and physics get pretty detailed. These are illustrations of the *applications* of Wide Computing, not essential to the understanding of Wide Computing itself. Similarly, there are lots of code snippets in the book (and a few complete breakdowns) but these are for reference. You can blow past them in a first reading, and go back when you are actually building code.

# 1.4 Drill down

### 1.4.1 Wide Computing is general and practical

The ability to do any computing task with Wide techniques follows from an even stronger claim: "You can do anything with Transputers in occam." The Transputer was a 1980s-era embedded chip designed to be programmed in

Wide fashion by its native computing language, occam. On the scale of Wide to Deep, occam is more extremely Wide than Connel or the techniques I will be teaching here. Nonetheless, correcting for the hardware capabilities of its era, Transputer-based solutions showed themselves capable of doing everything. Perhaps the most extreme example is in [5]: an autonomous vehicle travelling the German autobahn in 1993, guided by Transputers programmed in occam.

Though the Transputer is gone, occam still exists. It will be the foundation of the pseudocoding technique taught later in this book.

Some questions now arise.

If modern languages are too Deeply layered, and occam is only to be used for pseudocode, how are we to code our Wide programs?

This is a difficulty I have dealt with for years, and the solution, though not entirely satisfactory, is to use the least abstract language univerally available: C. Consulting Table 1.1 shows that C is already Deep (for instance in its use of a stack), but it is minimal and close to the bare metal. Communication using C libraries is completely general, not restricted to designed-in features as in many more recent languages. Hiddenness can be avoided, as discussed later, by not using malloc or C++ constructs.

Having settled on C, it turns out that the standard operating systems Linux and Windows can be adapted to Wide programming. This is because they have been forced to be server-friendly (even Windows had to restore its commandline BATCH-like capabilities because of this). Embedded programming is naturally Wide and, even if the tools available are more rudimentary, can be made to join the model, as long as they are programmed in C so that their communication features can be placed outermost.

What I avoid, or at least must work around, are object-oriented languages and their enforced hiding, as in this code snippet on page 4 of [9]:

```

void draw() {

w.step();

w.display();

}

```

This is in Processing, a language developed from Java. I asked William Swanson what he thought w.display() does, and he replied, "Magic."

What about code reuse, and economizing programmers' time?

To train C and these operating systems to do Wide Computing, I developed Connel. Used in a strict pattern, clearly modelled on occam, Connel forces the C program to behave in a reliable and understandable Wide fashion. Not only is this code highly reusable, but it relates to a clear data flow model. Knowledge of difficult C and OS-based communication behaviors is encoded in the Connel routines and does not have to be rehashed each time the programmer needs it.

The C code generated by Connel and other Wide Programming techniques is verbose. I do not have the resources to develop a scripting language, though C macros could be used to vastly reduce the number of lines of code. The resulting code blocks, which are completely standard C (not C++) and do not use malloc, must force the programming to do Wide tasks which are "stepchildren" of the stacky design of C.

The programmer's time spent on this, however, is minimal. This is because big blocks of code can be lifted from older programs, starting with the sample programs in the Connel distribution. For those who do not have a fold editor, cut and paste works fine. The upshot is a template program in which all the communication "pudding" is already working at full speed and can be tested, even before the algorithmic "plums" are inserted.

Why spend time on communication links when we could be writing real performing code?

There are three answers, and they get to the heart of the technique.

First, in any project, it's a good idea to do the hard part first. Communications are tricky, with complex state machines full of exceptions. A "path through the minefield" should be found. Doing "plum" code first, making assumptions about the comms, and later finding them wrong, can create a real tangle.

Second, the outer connector links can be accessed later without rewriting the program. This is useful for testing, for spying data flows, and for adding new features.

Third, the timing and dependencies of the algorithmic code are usually known before it is written. This means that a template "pudding-only" program can be made quite realistic (using timers and busy loops) and be available to help with construction of other pieces, at the same time as the algorithmic code is being written.

#### 1.4.2 Theory and Critiques

The contrast between Wide and Deep models of computing is the contrast between naturalism and legalism. This makes it clear that both models are universally valid for all programs. Legalism proposes that every action of the machine should be exactly in accord with its programming, and this (short of physical disasters) is always true. Naturalism proposes that every piece of the machine behaves according to the physical laws of its construction, and this also is always true. It is therefore always a matter of emphasis. The legalistic, Deep model says that the state of the program (data and code) carries within it, as a logical consequence, the output of the program. Thus, if Sum produces the sum of two positive integers, and LargestPrime produces the biggest prime number less than or equal to a positive integer, then

```

result1 = Sum(384290, 1289721) and

```

```

result2 = LargestPrime(43982576)

```

each fit this model. Creating the computational machinery to find the answer may not be so trivial (especially in the second case), but it is in principle doable. This is the viewpoint of functional programming.

Two problems arise.

(D1) First, what about computing time? The functional programming model ignores it, but it matters in the real world.

(D2) Second, what if not all the state is present at the time the task is triggered? Then delays and communication calls (like "read(x, y)") will have to be sneaked in to achieve success.

The naturalistic, Wide model says that any machine consists of pieces, each of which is itself a machine, which has an initial state, a final state, and ways of affecting the machines or results around it. This is the viewpoint of occam, of hardware design, and of engineering outside the computing world (as of bridges and classic cars).

From the standard software designer's point of view, a choice of two difficulties arises.

(W1) If the machine is programmed in a standard algorithmic fashion, especially with dynamic resources, it is hard or impossible to disentangle the smaller machines and their effects on each other.

(W2) On the other hand, if Wide techniques are used to isolate the smaller machines except for specific, known communications and timing effects, it seems that a crippling restriction is imposed on the options available to the programmer.

There is one weak point in each criticism—one path through which the model's advocates can break through.

(D1) is weak under conditions of Moore's Law, with rapidly increasing raw computing speed. Succeeding advances in chip speed have permitted Deep Computing to sweep all before it until very recently. Lately, the complexity explosion implied by (D2) has begun to take its toll.

(W2) is weak under conditions of cheap computing resources. GPGPU and map-reduce are already demonstrating this on the fringes, and non-uniform memory access (NUMA) is pressing it into center stage, but it is still viewed more as a problem than an opportunity. In fact, it is very much an opportunity, because of a second-order effect I have not discussed yet.

In Deep computing, by the very fact that all programming options of the major machine are left open, any part of the program can affect any part of the machine, no matter how distant its functionality. (This is a trait of legalism: some weird codicil can make the Alternative Minimum Tax apply to a low-wage worker, so everyone needs to check everything all the time.) This means that programming effort and complexity increase as a function of what every other programmer has done everywhere else through all of history. Also, internally, as a program's size increases, its difficulty increases nonlinearly because of the entanglements.

In Wide computing, on the other hand, every piece is self-contained and unaffected by history. The difficulty of expanding a program is linear. *This* is an effect that shows itself very early, even in programs maintained by only one person. All that is needed is to figure out how to apportion the work among the independent pieces, using planned communication paths, without significantly affecting total efficiency. And great leeway is offered by modern hardware, which now cheaply offers more and more cores that can work side by side, instead of attempting to increase clock speed.

#### 1.4.3 Knowledge, hiding, and predictability

Before going on, I must issue a warning to readers who are not quite so naive in the terminology of Computer Science (CS). Many common terms are in use in CS, especially in object-oriented programming (OOP), in a way that means almost the opposite of their naive meaning. Understanding this is critical to critiquing and understanding Wide Programming.

I use the word "piece" because both "object" and "component", which seem that they should mean the same, have become tainted in this way. They refer more to namespace entities than to physical things or analogues thereof. In particular, their "methods" are designed to *hide* the "plumbing" through which data and timing are transmitted. Consider the line

w.display();

in the Processing example I quoted from [9].

Inheritance and polymorphism increase this hiding effect. The result is ease of programming, but only up to a point. This point is reached when lack of knowledge takes its toll. Code workarounds and branches are then necessary, but increase the problem for later rounds of coding.

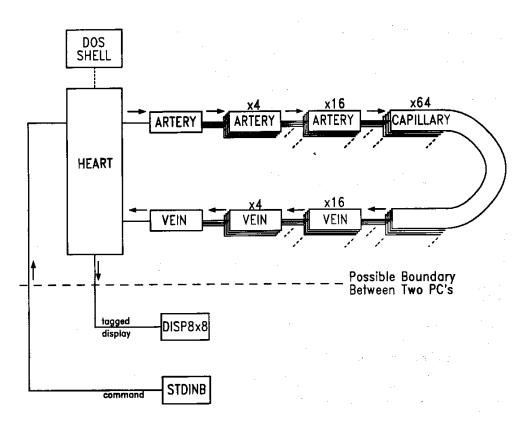

Figure 1.7: HEART3 1MB Palmtop DOS demo

The design in Wide Computing is done the opposite way. Stuff happens within a piece, but it is deliberately set up so that all significant effects that cross the boundary of the piece, both in time and "space," are known and explicitly enumerated. (Notice that this is how all engineering is done outside the computing world.)

An important consequence of this is *hardware/software equivalence*: It does not matter whether a piece is implemented as a separate piece of hardware (multiprocessing), or as a Wide-designed program or process sharing code and timing within a single piece of hardware (multitasking), as long as the resources are sufficient. The significant effects are the same. Therefore these options are interchangeable. As [6] says (page 71): "Configuration [meaning how the processes are mapped onto hardware] does not affect the logical behavior of a program."

This huge claim—whose consequences you can well imagine in the world of massive multicore, GPGPU, and Google-scaled map-reduce—was illustrated

by my 1993–1996 work of [3], in which DOS, which is a single-tasking OS with only one megabyte of memory, was tricked into multitasking on the HP Palmtop. Figure 1.7 shows a tiny example (it was extended to up to 128 simultaneous "screens", either multitasked or multiprocessed). The switch between multitasking and multiprocessing is achieved *without recompiling*.

Because all the significant effects going into or out of a piece are programmed on the outside, each piece can be tested separately, and connected pieces can be spied upon as they interact. More important, knowledge about what the piece does is always preserved, no matter how many generations of software development follow. And a piece's behavior is not silently altered by some internal call whose definition is changed by a later version of library or OS. Wide Computing restricts itself to stable, low-level tools.

It remains, then, to answer objection (W2) in more detail. First I will sketch some basics.

#### 1.4.4 Data flow basics

The consequence of dealing with objection (D2) is the concept of *data flow*. This obviously points to an analogy with fluid flow, but we need to justify this.

A resource, such as memory, may have a necessary role in causing a computing machine to put out the correct result. Here we are concerned with a resource that is *writable* in the context of the program. This implies that at one time (before being written to) it may have a different state from later (after being written to).

If this change of state involves progress in setting up for a correct program output or behavior, then clearly in some sense the "after" state must be better than that "before." Data flow happens when the resource changes from an indifferent state (either undefined or useless) before to a specific and useful state after. If it's a byte of eight bits, then any of them can be either 0 or 1 before, and we don't care. A full-byte write puts each of them into a specific state (either 0 or 1, but decided correctly).

Typically (but not always) this state is a copy of the state of a similar byte somewhere else. Then it is said that *data has flowed* from the *source* byte to the *destination* byte. Notice that in the case of a "copy," the analogy with a flow is not exact, because afterward the data still exists in the source byte.

It is possible to have a "move," in which the source byte degenerates to an undefined or useless state. This could be modeled as a turntable with a byte on each side turning 180 degrees. More commonly, it may happen that the source memory is not used further with that value after its data has moved on, and waits to receive more data from yet another source before being useful again. This would then be part of a "pipeline." But in general we cannot necessarily assume this, and the term "data flow" permits one-to-many copies and refers specifically to the advancing state of the receiver.

A critical part of data flow is its *timing*. Use of the data may not start until after it has flowed in. (Failure to assure this is a common source of program bugs.) In fact, transmission of a timing event alone is a form of data flow. It changes one bit of information, causing "After event?" to change from FALSE to TRUE. Even though no bit of memory may contain "After event?", this change is capable of affecting program flow, as by an interrupt. Therefore the term "data flow" is synonymous with "timing and data flow."

A final point is the pipeline model of data flow. In fact, in all the ordinary output/input combinations (voltage on a wire or wires, transmission through wave action, writes to memory) the datum input rubber-stamps the datum output, and the time received is substantially the same or at least in time order of sending. This substantiates the usual model of ordered pipeline flow.

The modelling of programs as collections of single sequences of actions which can emit or receive data or timing signals to or from other such sequences was pioneered by C.A.R. Hoare in Communicating Sequential Processes, or CSP. The computing language occam was modeled on CSP, and the Transputer embedded processor was built to run occam.

However, occam IO is synchronized and unbuffered (with one exception: the first byte sent through a wire link). Due to the difficulties of coding explicit FIFOs everywhere, most standard data channels are ordered and buffered. A number of outputs may be standing in a queue, not yet input by the receiver. Because Connel is designed for practical use, we go with "ordered and buffered" even in our "almost-occam" pseudocode. It is always possible to create the synchronized and unbuffered design if necessary by using an explicit acknowledge (ACK) message going in the opposite direction to the main one.

#### 1.4.5 Algorithmic basics

The great challenge to the Wide Computing model in (W2) is algorithmic efficiency. By deliberately limiting the ability to influence other pieces of the general program, the Wide programmer has reduced his options in performing the task. This includes not only branches and writes to the alien pieces, but even reading information from an alien piece, if that information is either subject to change (race condition), or is too far away (NUMA). Therefore special program or hardware elements called *communication channels* come to the fore, and are used to move data from one piece to another.

Thus the two main efficiency challenges to Wide Computing are:

(C1) Is the burden of data transmissions (called "communications overhead") required by the Wide algorithm so great that the system is bogged down by it?

(C2) Even apart from communications overhead, is the restriction enforced on the design of the algorithm itself so that its work can be done in several independent processes (called "cost of parallelization") so great that it ruins performance?

The answer, of course, is, "It depends." The goal of the Wide Programmer is to find as many tasks as possible for which these challenges can be met. And the surprising thing is how many of them there are. The fact is that raw size makes problems more parallelizable, *often by the crudest methods*, even when by nature they are very entangled (like a compiler parse).

I will explore three dualities in the world of algorithms. They are related but not identical. Then I will give a simple example, that shows how parallelizability can creep in where not expected.

First duality: top-down versus bottom-up. This is usually a duality of design. In top-down design, the large-scale problem pre-exists the small-scale components used to solve it, and usually determines their character. In bottom-up design, the small-scale components are a "given" and by connecting them (or a subset of them), the large-scale solution is found.

Second duality: intensive versus extensive. This actually refers to physical units, but I'm using the terms more naively to refer to those problems where the interconnections are relatively very numerous compared to the amount of data (intensive), as opposed to those with few or no non-local interconnections between massive data (extensive). An example of the first might be a deep expression evaluation:

```

x = (((x1+x2)*(x3+x4))+((x5+x6)*(x7+x8)))/((x9-x10)*(x11-x12))

```

An example of the second might be a multiply-accumulate:

w = (y1\*z1)+(y2\*z2)+(y3\*z3)+(y4\*z4)+(y5\*z5)+(y6\*z6)

Frequently, intensive expressions hide what must be an extensive implementation. An example is the recursive definition of factorial:

```

unsigned integer fac(unsigned integer n) {

return (n > 0) ? n*fac(n-1) : 1;

```

#### }

Unwinding the evaluation of this formula reveals that an array or stack of n "black boxes" is needed. A bottom-up approach is more economical:

```

unsigned integer fac(unsigned integer n) {

unsigned integer k = 1;

unsigned integer i;

for (i=1; i<=n; i++) k *= i;

return k;

}</pre>

```

The third duality is deep versus wide, as defined above. An intensive problem could be analyzed by top-down methods and performed by deep techniques, with a single "outer face" and "black boxes" which, each in their turn, are resolved into deeper problems with black boxes until finally they have real data that can be evaluated. (This is how compilation is typically done.) An extensive problem with a repeating bottom structure can do those evaluations first and then combine them. (This will work for the multiply-accumulate or dot product.) Thus intensive problems tend to be recursive, stacky and deep, and extensive problems array-oriented and wide.

However, an array-oriented extensive problem may have an order imposed on its resolution, in which case a wide approach may be harder to find. An example of this is standard long division. Even in these cases, when a large number of similar calculations are required, vector (pipeline) programming makes Wide computing usable.

#### 1.4.6 Algorithm example

I will now fully analyze one apparently simple problem, showing how subtle these issues can be. It is addition of two unsigned binary integers.

| cin | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  |

|-----|----|----|----|----|----|----|----|----|

| a   | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

| b   | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  |

|     |    |    |    |    |    |    |    |    |

| sum | 00 | 01 | 01 | 10 | 01 | 10 | 10 | 11 |

The above table shows the complete single-bit results, including a carry-in. The left bit of the sum is a carry out, the right bit the modulo sum. Two N-bit numbers can be added, giving an N-bit modulo sum and one carry out bit, by feeding the carry out of sum K into the carry-in of sum K + 1. This is an extensive algorithm, the "ripple carry," but due to the order of dependency it takes time N.

Now we carry out a top-down analysis. If **a** and **b** are N-bit integers, and **c** is 0 or 1, then we define

#### s(a,b,c) = a+b+c = c(s(a,b,c))|m(s(a,b,c))

where c is 1 bit and m is N bits. Here | does not refer to "or" but is a join between left bits and right bits in a binary number, so that

1b|0100b|1001b = 101001001b

for example.

If N = 2M, a = aL|aR, and b = bL|bR, then the carry out of the aR+bR sum is the carry-in of the aL+bL sum. Hence we get

```

s(a,b,c) = s(aL,bL,c(s(aR,bR,c)))|m(s(aR,bR,c))

```

Hence if we have the four incoming values (with their carries out) of s(aL,bL,0), s(aL,bL,1), s(aR,bR,0), and s(aR,bR,1), we can construct s(a,b,0) and s(a,b,1) by selecting one of the left sums based on the right carry, and then throwing away the right carry.

In fact, since  $c(s(aR,bR,0)) \leq c(s(aR,bR,1))$ , we can copy s(aL,bL,0)over s(aL,bL,1) if c(s(aR,bR,1)) == 0, and we can copy s(aL,bL,1) over s(aL,bL,0) if c(s(aR,bR,0)) == 1. In the rare case where the two right carries disagree (which only happens if aR and bR are bitwise complements), we need do nothing.

Carrying this logic all the way down to the single bit adds, we discover that with enough parallel adders, we can finish our addition in  $\log(N) + 1$  steps instead of N steps. Here  $\log(N)$  is, as usual in CS, the log base 2 rounded up to an integer. This "conditional sum adder" is as good as the best adders in use in actual hardware, such as the Kogge-Stone adder.

For those who are conversant with the problems of transistor-level chip design, I may add that with one extra step, every carry bit can be made to agree with the carry out of s(a,b,c) for the two maintained sums. This eliminates fan-out problems and breaks the data at each reduce step into independent sets of eight bits, two of which are neither read nor written.

This adder is a trivial example of the "map-reduce" approach to parallelizing problems. This, where applicable, reduces a problem of size and time N to a problem of parallel size N and time  $\log(N) + 1$ . The "map" part is the bunch of parallel operations (time 1) and the "reduce" part is the joining of the results (time  $\log(N)$ ). For example, a problem of size 256 is done in time 9. Most really large problems are either outright local and hence completely parallelizable, or susceptible to map-reduce, which by being a little wasteful in transistors (cheap) is able to save immense amounts of time (very valuable).

#### 1.4.7 The Connel crawl-space strategy

I will conclude this chapter by returning to questions of practicality.

The purpose of this exercise in Wide Computing is to put scientific computing power, equivalent to the actual ability of the hardware that is so cheap nowadays, into the hands of ordinary "hackers." In particular, it should be possible to open the gates to a yard as big as you want—working from the problem that you want to solve, and not from the capabilities of available UIs, "apps" or languages.

So I don't care if I waste a few cycles, or generate a few extra lines of code (though I do not want to waste the programmer's time). And I am not anxious to keep everything up to the purest occam-level CSP standard. All I want is that it should work, and it should be obvious why and how it works, and all the working bits and pieces should be easily and clearly accessible.

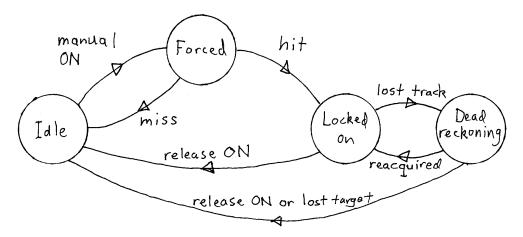

Connel doesn't do threads, but it does select(). Connel stays coarse-grained, adapted to C machines and operating systems, and remains in the realm of full processes. If shared memory is needed, it's kept under control of terse negotiating commands sent over the standard, explicit communication channels. You don't get responsiveness by using fine-grained threads, you get it by using select()—a fact that seems to be forgotten even by hardware designers these days (e.g. Arduino).

The CSP people discovered decades ago that there is no substitute for **select()** (called ALT in occam) when you have a single process that needs to respond to several asynchronous communicating partners. Without it, you can spawn fine-grained threads until the cows come home, and you will still get hesitation. The coarse processes spend a moment starting, but then respond just as fast. They are understandable, and there are not many of them. And all the OS tools help you keep track of them, and Connel spies can watch the data.

Connel select also supports timer expiration. The newest development of it is capable of supporting graphics events, either in Windows or in Linux (XCB).

Connel deals with OS-accessible, named data channels. We have keyboard and screen, serial ports (including virtual ones via Bluetooth, USB and VMWare), Windows named pipes, and Linux sockets. We could do more, but that seems to be enough to get universal connectivity, both within an OS and between systems, including embedded.

Reconfiguration involving data channels of the same type does not require recompilation. Reconfiguration that changes the type of channel (say from socket to serial) usually requires only minor, methodical changes on the outside of the code, in the "pudding." This is all that is needed for changes from

#### 1. INTRODUCTION

multitasking to separate hardware assist, or from OS-based components to embedded ones—a prime use of Connel in a successful commercial software project.

This strategy puts all the difficulty of communication hookups firmly on the outside and at the start of development. Take lots and lots of detailed notes! Make HOWTO files, and keep adding to them! Then you will come back months later and boot up all the pieces of your complex system in proper order, and it will work, and you will know why.

Multiple terminals and scripts are your friends. This is the easiest way to develop code either in Windows or Linux. Again, take lots of notes, and avoid the trap I have fallen into—which is to rely too much on history files. This is especially seductive in VMWare virtual machines, which suspend and therefore never shut down.

Using redirected spies and dummies permits you to send and receive data at full speed. Accurate timing reads—which can be arranged at microsecond accuracy using RDTSC—can be used to detect even the smallest hesitations. Simple command-line programs can do fast post-mortem analysis of the redirected output and spy data.

Design sketches (First Wave) and pseudocoding (Second Wave) are critical to any project. The Wide Computing approach is front-loaded with enough design to make sure of the power to finish the job. Each piece gets its sketch, and is a live thing that pulls in input and pumps out output with a certain rhythm during its lifetime. You are never caught short because you add enough CPU and communication to make sure of staying ahead of the demands of the task.

Wide Computing offers a number of rather obvious top-down techniques for project design. There is simple worker parallelization for completely distributed tasks, like CDMA channels or the well-known prime searches. There are partly distributed map-reduce calculations, as in the above example, and pipeline calculations. In the latter case the workload may break down into large chunks, with an alternating communication and computation "breathing" structure that produces batches of output at a varying delay. See [10] and related references. Finally, and most obviously of all, there is the breakdown of a project into parts of different kinds, which are then handled by different pieces with needed data passing between them, as in Figure 1.2.

All of the above are used as needed until each piece is clear enough so that a bottom-up analysis of the piece estimates its computational needs, communication bandwidth, and delays. Then it's all combined and a total estimate made. This works over the whole lifetime of a project.

Long-lived projects find themselves using the last technique (parts of dif-

ferent kinds passing or shunting data flows) more and more as features are added. An example would be a movie editor with inventive feature addition. Dummies (that pass data and do nothing) are your friend during such addon developments. These include insertion of new hardware that passes data much faster than needed without changing program behavior until their added capacity is used.

The key thing about Wide Computing is that there is no point at which increasing complexity locks up the project. Each updated replacement piece, even if of completely different design and date, is slipped in to perform according to the same specifications as the old, like a new alternator replacing an old alternator in a classic car. Then a new capability can be spliced in without disturbing the old. It's like a village expanding into a city, and yet "Chicken Street" remains.

#### 1.5 References

. . .

[1] Alboaie, Sinica: "Harvests: From now is possible to call asynchronous functions in a declarative way and to get almost the same experience as with synchronous code," GitHub, circa January, 2014.

https://github.com/salboaie/harvests README.markdown

Harvests library is an experiment to sort out the ugliness of the asynchronous callbacks without promises or control flow libraries.

//on success harvest.myFileContent will contain the content

//you can start as many calls and they will be executed when

their dependencies are fulfilled

- Choisser, John P., and John O. Foster: The XT-AT Handbook. Annabooks, San Diego, 1989–1992. Booklet (3.5" by 6"), 94 pgs.

- [3] Dickson, Lawrence J: "occam (TM) Road Map for the DOS PC." Proceedings of the 1996 International Conference on Parallel and Distributed Processing Techniques and Applications (PDPTA'96), Hamid R. Arabnia, editor. CSREA, Sunnyvale CA, 1996.

- [4] Dickson, Lawrence J.: "Transparent Analogy as a Foundation for Language," September 12, 2007. http://www.tjoccam.com/tacliwhp.pdf

- [5] Franke, U., and H. Fritz, A. Kuehnle, and J. Schick: "Transputers on the Road," Transputer Applications and Systems, Proc World Transputer Congress 1993, Vol 1, IOS Press 1993, p 1–17.

- [6] INMOS Ltd: occam 2 Reference Manual. Prentice Hall International Series in Computer Science, C.A.R. Hoare, editor, Prentice Hall, 1988. http://www.transputer.net/obooks/obooks.asp

- Justo, George R. R., and P. R. F. Cunha: "Deadlock-Free Configuration Programming," 2nd Int. Workshop on Configurable Distributed Systems, March 21-23, The IEEE Computer Press, pages 147-158, 1993. http://www.cpc.wmin.ac.uk/~justog/GeorgeJusto-Publications.html

- [8] Roscoe, A. W.: Understanding Concurrent Systems, Texts in Computer Science, Sprinter, 2010.

- [9] Shiffman, Daniel: The Nature of Code. http://thenatureofcode.com, 2012.

- [10] Welch, Peter, and George Justo and Colin Willcock: "High-Level Paradigms for Deadlock-Free High-Performance Systems," *Transputer Applications* and Systems '93, Volume 2, IOS Press, 1993, p 981-1004.

http://www.cs.kent.ac.uk/projects/ofa/kroc/high-levelparadigms-1993.pdf

This is a beautiful and intuitive solution for any number of problems, deadlock-free. Vertically there is a client-server cascade, and horizontally a massively parallel "heartbeat" system, with hybridization, therefore control and status, possible. All results are proven, though the CSP terminology may require some study. See [8].

[11] Standish, Stacey: Mathematics and Computer Science employment statistics (communication). Bureau of Labor Statistics, 2006.

Lamoreaux, Naomi R, and Kenneth L. Sokoloff: "The Decline of the Independent Inventor: A Schumpeterian Story?" 2005.

Odlyzko, Andrew: "The Decline of Unfettered Research." AT&T Bell Laboratories, October 4, 1995.

Wikipedia: "List of Intel Microprocessors," 2006.

http://www.sparcproductdirectory.com/history.html ca 2006.

Viscosity = Effort/ROI indexed from 1966, Cobb-Douglas Production Function (geometric mean) with labor weighted 75%, total workstation computational power 25%.

### First Wave: Design The Major Pieces

#### Abstract

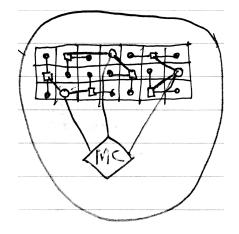

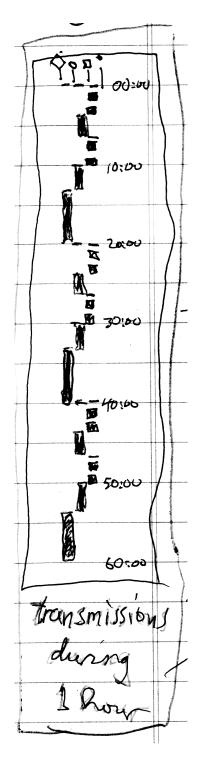

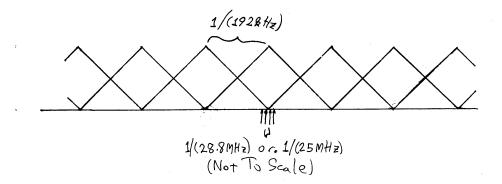

The purpose of this chapter is to describe the First Wave of Wide design, which consists of wrestling with the problem from a Data Flow point of view until it is clear that we have a path leading to a successful solution. I will illustrate with two real-life examples: the timed display of an array of temperature and humidity sensors in an orchard (thank you, Roger Wagner), and the CDMA decoding of signals from 120 weakly transmitting satellites (thank you, Rob Fryer). Each of these will suggest further needs which will be worked on in later Waves.

#### 2.1 First Wave technique

The First Wave does not yet involve coding or even pseudocoding, though it may involve the study of existing code and pseudocode. It is focused instead on issues of intense practicality. You do not exit the First Wave until you are confident that the tools you have settled on are sufficient to solve the problems presented by the project.

This requires primitivism: data flows, timing, and cycle counting. But it also involves drawing pictures and diagrams that help make clear what the demands of the problem are. The standard technique of counting up the time required by the central calculation and multiplying it by the data rate is, as experienced programmers know, not good enough. Issues such as delays, data rate irregularity, and dependencies have to be faced clearly.

In a problem of any complexity, you will not escape without dealing with priorities. Calculation has to take place, but data needs to get in to be calculated upon, and the results have to get out. These operations create resource contention, and the tools and chips to be used have to be measured up against their needs. Otherwise as simple an operation as serial input could trip you up, especially in embedded work. As a rule, the first step in prioritizing is to place essential communication at a high priority, calculation at a lower.

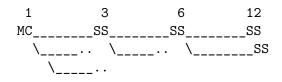

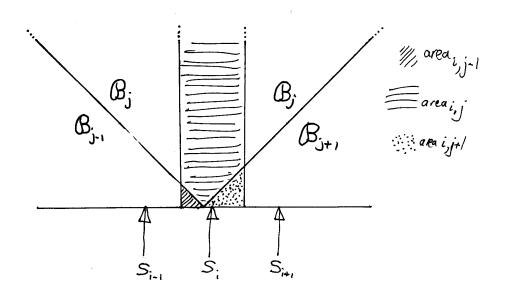

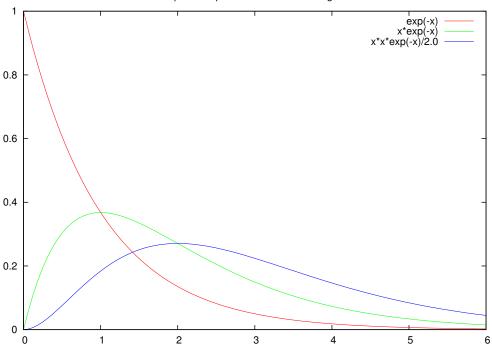

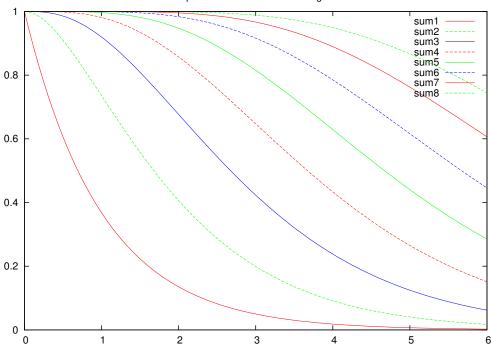

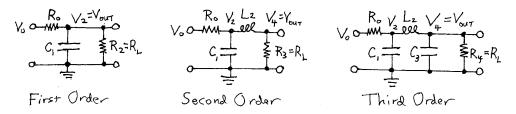

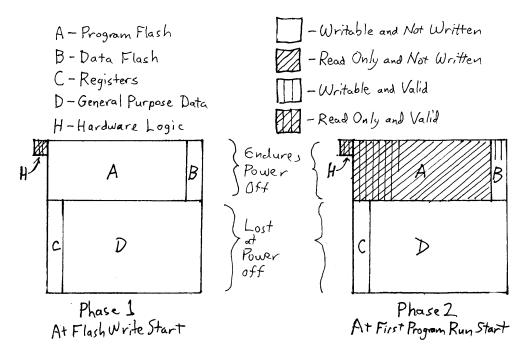

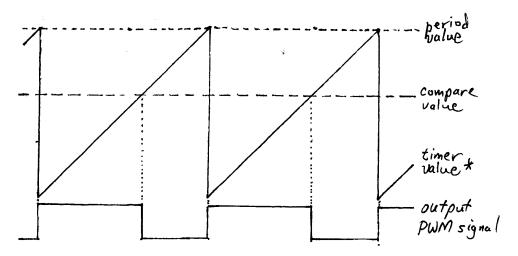

The key to success is breaking up the problem into simpler parts. These are Wide Computing pieces, not dependent calls or methods. A piece stands alone and is equivalent to a piece of hardware. It starts, inputs data and timing according to a certain rhythm, outputs data and stimuli with a certain rhythm, and ends. The methodology of getting from input data to output data can be left vague, as long as the dependencies and effort required can be conservatively estimated.